SystemVerilog para FPGAs

Enfocado a brindar toda la sintaxis básica de SystemVerilog para diseñar circuitos digitales, así como una introducción a la verificación usando testbenches. Aprenderás el manejo Quartus para la Síntesis e Implementación en una FPGA de INTEL.

¿Para quién esta dirigido este curso?

Para estudiantes, profesionales y entusiastas de la electrónica digital que deseen dar el siguiente paso en el diseño de hardware.

Es ideal para quienes ya tienen conocimientos básicos de sistemas digitales y quieren aprender a programar FPGAs utilizando SystemVerilog, un lenguaje moderno y potente ampliamente usado en la industria.

15 horas de duración

Nivel Intermedio

Syllabus SystemVerilog para FPGAs

Entrena las habilidades necesarias para diseñar y verificar sistemas de hardware complejos utilizando SystemVerilog y FPGAs

Clase 01

Introducción al Diseño Digital con FPGAs y SystemVerilog

Clase 02

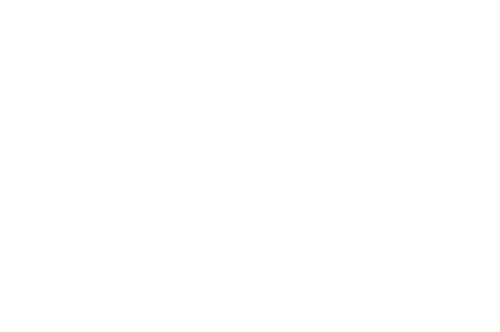

Asignaciones, Control y Estructuras de Código en SystemVerilog

Clase 03

Verificación y Simulación en SystemVerilog usando Testbenches

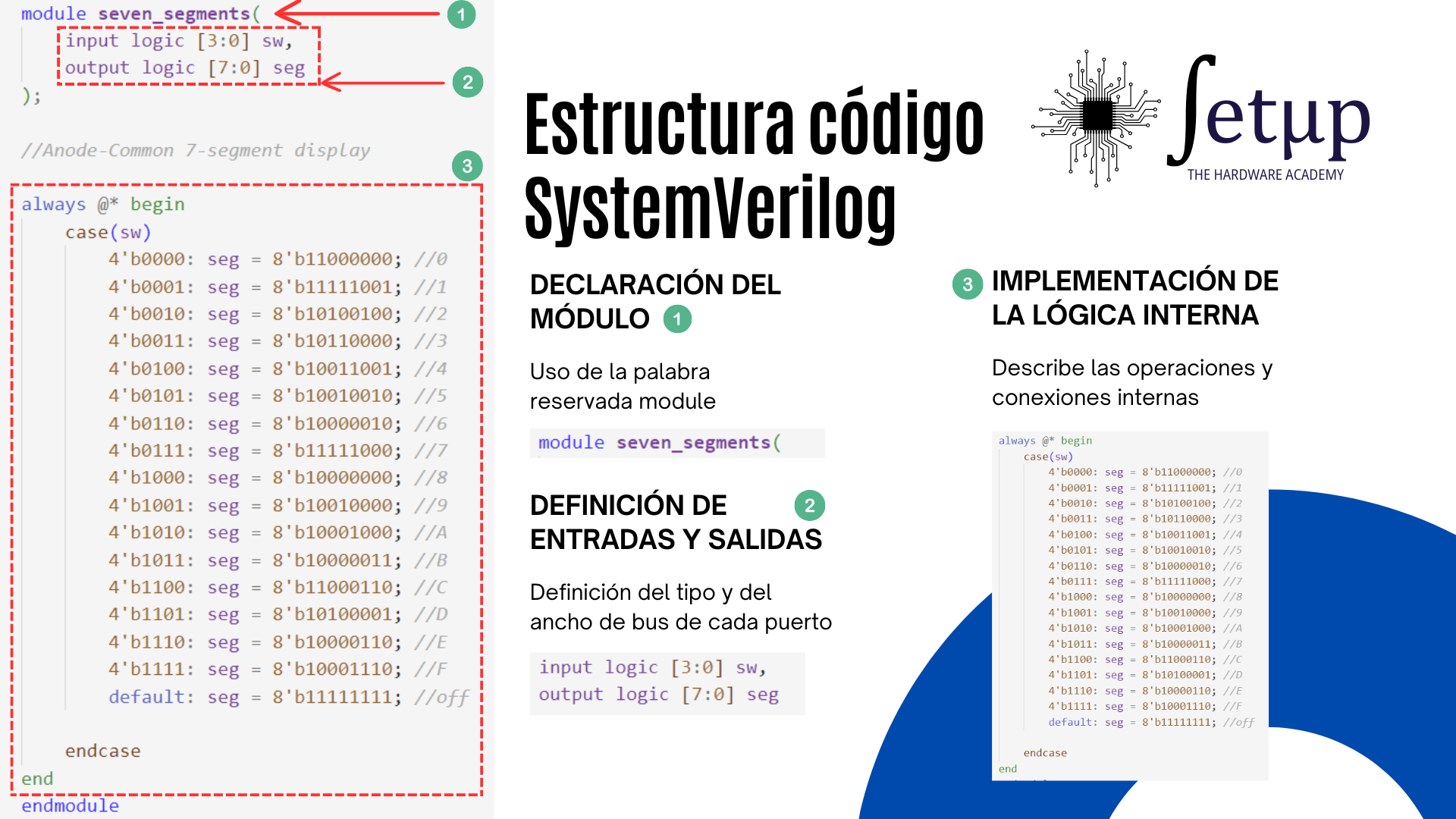

- Lista de Sensitividad

- Asignaciones Bloqueantes

- Asignaciones No-Bloqueantes

- Bloque initial

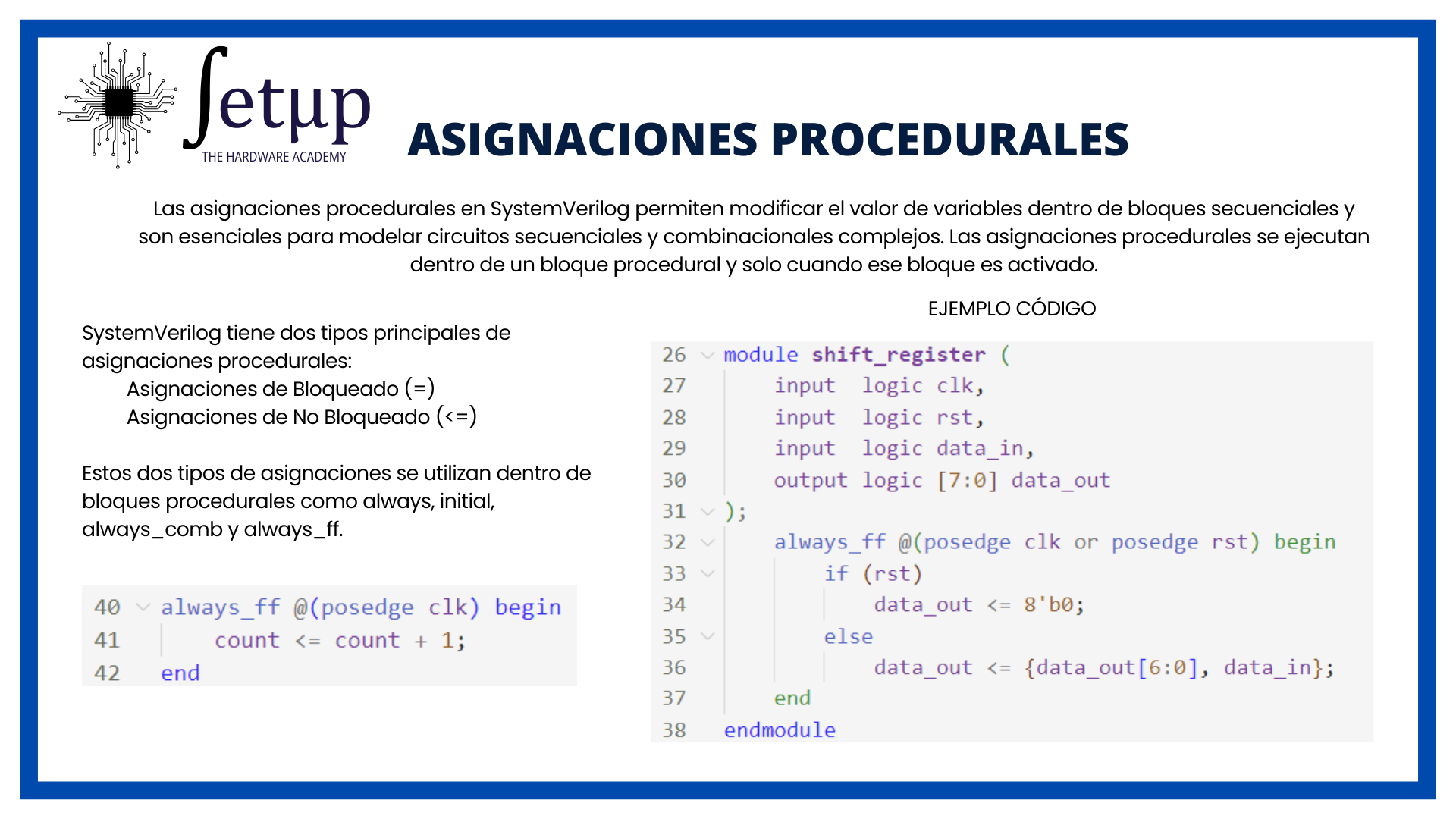

- Testbenches con SystemVerilog

- Generación de clock

- Testbench Mux 8:1 y Unidad Aritmetica Lógica

- Testbench Sumador de n bits y comparador

- Lab: Shift Register y Contador con control

- Testbench Shift Register y Contador con control

Clase 04

Modularidad, Manejo de Memoria, Funciones y Tareas en SystemVerilog

- Funciones en SystemVerilog

- Tareas en SystemVerilog

- Testbench con tareas

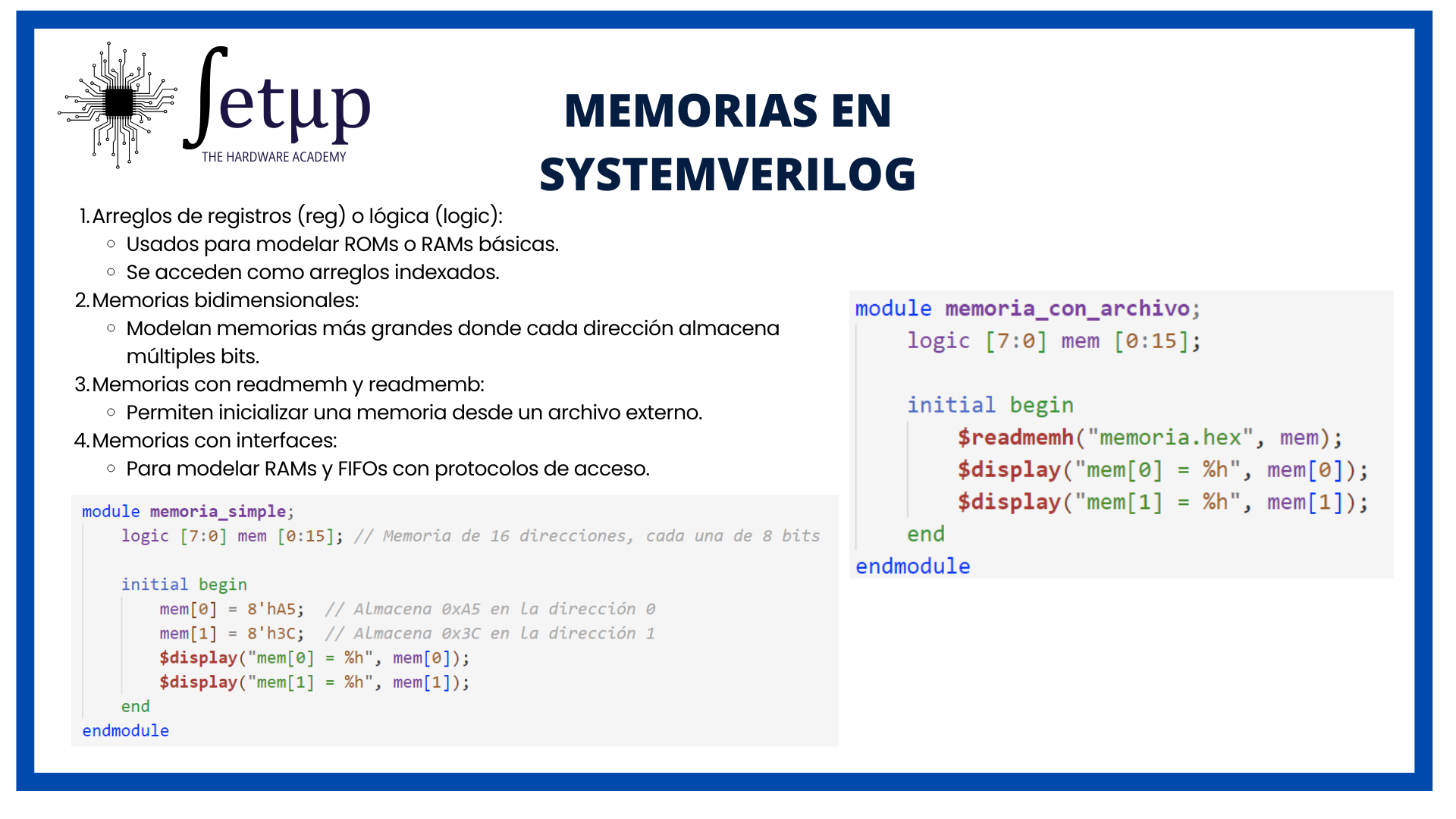

- Memorias con SystemVerilog

- Escritura y Lectura de la Memoria

- Uso de generate en SystemVerilog

- Código Parametrizado en SystemVerilog

- Código Jerarquizado en SystemVerilog

- Lab: First Input First Output en SystemVerilog

- Testbench FIFO con Memoria SystemVerilog

Clase 05

Máquinas de Estado e Interfaces

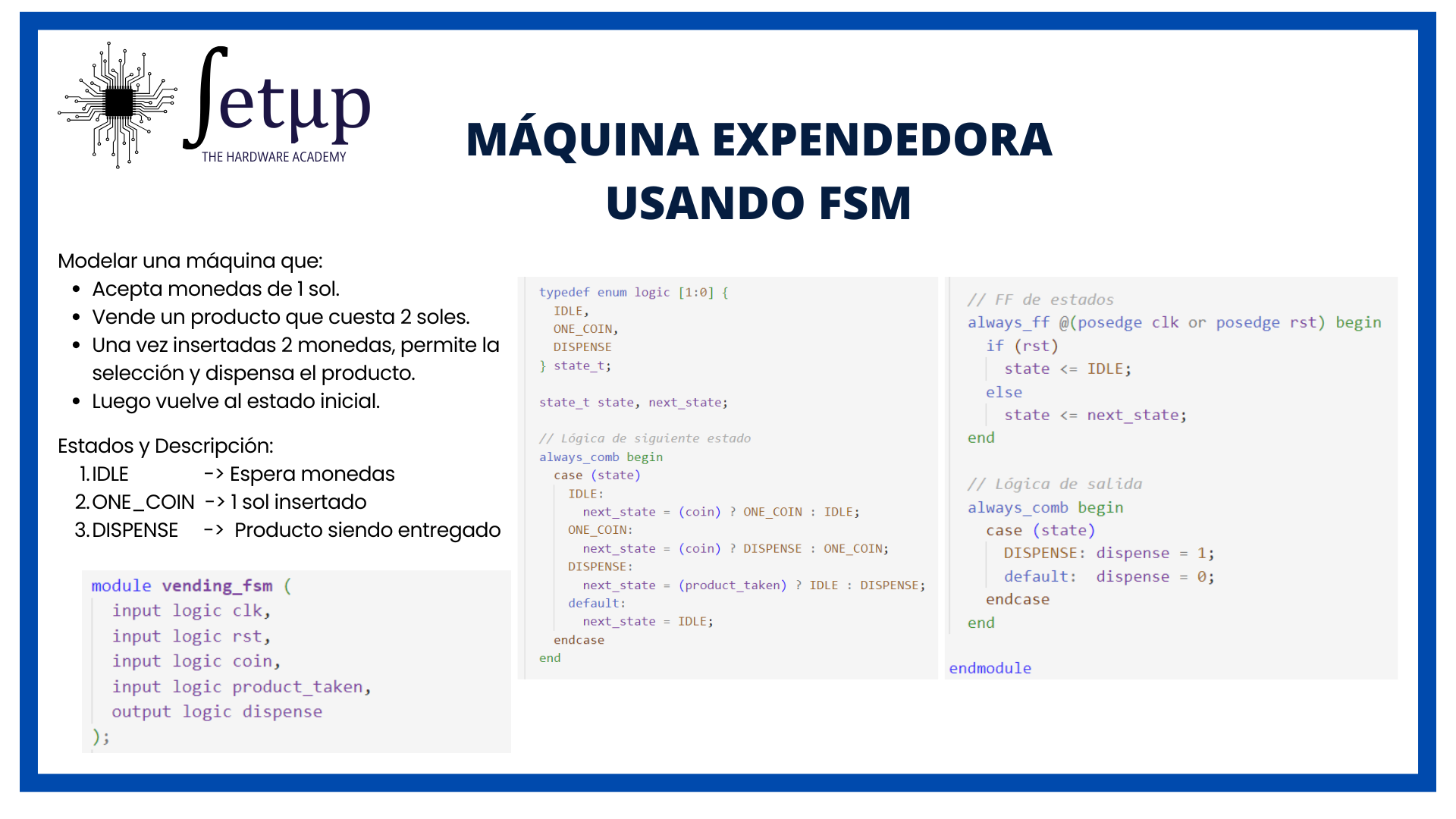

- Maquinas de Estado con SystemVerilog

- Lógica del Siguiente Estado

- Bloque de actualización

- Lógica para las salidas de la FSM

- Máquina Expendedora usando FSM

- Definición de Estados, Máquinas mealy y Moore

- Introducción a las Interfaces en SystemVerilog

- Interfaces con Modport

- Lab: FSM usando SystemVerilog y Testbench

- Integración de Interfaces en un Diseño Completo

¿Deseas más información?

Envíanos un mensaje al WhatsApp y te brindaremos más información!